#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

Disclaimer 🖃

## **Doctoral Dissertation**

# Design of Compact and Energy-Efficient Inverter-Based High-Speed Transmitter

Changjae Moon (문 창 재)

Department of Electrical Engineering

Pohang University of Science and Technology

2025

# 컴팩트하고 에너지 효율적인 인버터 기반 고속 송신기 설계

Design of Compact and Energy-Efficient Inverter-Based High-Speed Transmitter

# Design of Compact and Energy-Efficient Inverter-Based High-Speed Transmitter

by

Changjae Moon

Department of Electrical Engineering

Pohang University of Science and Technology

A dissertation submitted to the faculty of the Pohang University of Science and Technology in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Electrical Engineering

Pohang, Korea

12. 20. 2024

Approved by

Byungsub Kim (Signature)

Academic advisor

# Design of Compact and Energy-Efficient Inverter-Based High-Speed Transmitter

# Changjae Moon

The undersigned have examined this dissertation and hereby certify that it is worthy of acceptance for a doctoral degree from POSTECH

12. 20. 2024

Committee Chair Byungsub Kim

Collection @ pos

Member Hong-Jun Park

Member Jae-Yoon Sim

Member Ho-jin Song

Member Jaeyoung Seo

DEE

문창재 Changjae Moon

20192387

Design of Compact and Energy-Efficient Inverter-Based

High-Speed Transmitter.

컴팩트하고 에너지 효율적인 인버터 기반 고속 송신기 설

계.

Department of Electrical Engineering, 2025, 92p

Advisor: Byungsub Kim.

Text in English.

#### **ABSTRACT**

This thesis introduces design techniques for developing compact and energyefficient inverter-based high-speed transmitters for memory interfaces. The research is divided into two main components: a study on a novel feed-forward equalizing (A-FFE) transmitter (TX) architecture based on addition-only operations, and the development of a four-level pulse-amplitude modulation (PAM4) transmitter with crosstalk compensation (XTC) implemented with inverter-based XTC taps.

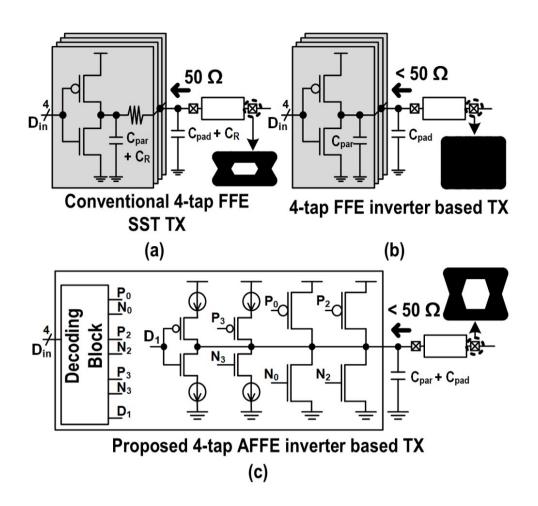

The first component presents an inverter-based 4-tap A-FFE TX designed for compact and power-efficient single-ended interfaces. Conventional FFE (C-FFE) TXs typically employ source-series terminated (SST) drivers; however, their linear resistors consume substantial area and introduce significant parasitic capacitance, compromising both power efficiency and output bandwidth. To address these challenges, we developed the A-FFE architecture, which eliminates subtractions between FFE taps

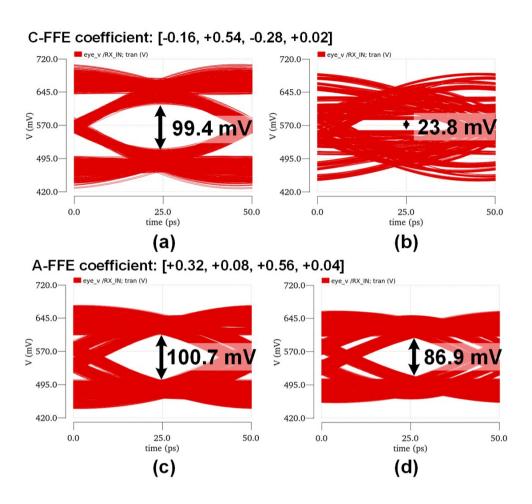

and enhances robustness to coefficient quantization errors. These improvements facilitate the implementation of area-and-power-efficient inverter drivers in FFE. The prototype, fabricated in 28-nm LP CMOS technology, demonstrates a data rate of 20 Gb/s/pin, achieving an eye height of 55.1 mV and an eye width of 0.44 UI over a 15 dB PCB trace, while maintaining power efficiency at 1.18 pJ/b and 68 % worst eye sensitivity. Notably, reducing the most sensitive FFE coefficient by 20 % resulted in only a 13.6 % decrease in eye-opening. The resistor-free design, utilizing inverter drivers, achieves a compact layout of just 1149 µm<sup>2</sup>.

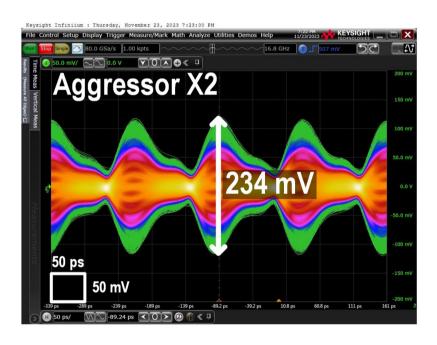

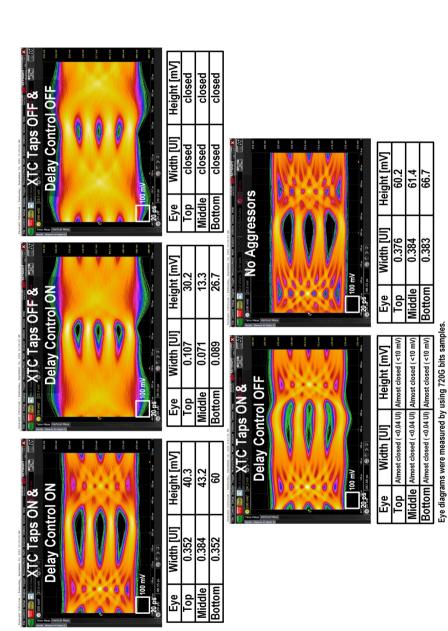

The second component introduces a PAM4 TX with XTC designed for short-reach memory interfaces. The design incorporates efficient encoders and transition detectors to recognize crosstalk-inducing patterns and control inverter-based XTC taps accordingly. Precise gain and delay control in the XTC system minimizes compensation errors arising from mismatches between victim and aggressor channels. Implemented in 28 nm LP CMOS technology, the TX operates at 16 Gb/s and demonstrates significant performance improvements with XTC enabled, showing 203 % and 396 % increases in eye height and width, respectively. This area-efficient design, employing inverter-based XTC taps, requires only 0.0067 mm², resulting in an area per data rate of 0.00042 mm²/Gbps.

# **Contents**

| I.  | Int   | roduction                                                               | 1  |  |  |  |  |  |  |  |

|-----|-------|-------------------------------------------------------------------------|----|--|--|--|--|--|--|--|

|     | 1.1   | Motivation                                                              |    |  |  |  |  |  |  |  |

|     | 1.2   | Application and Problem Overview                                        |    |  |  |  |  |  |  |  |

|     | 1.3   | Thesis Contributions                                                    |    |  |  |  |  |  |  |  |

|     | 1.4   | Thesis Organization                                                     |    |  |  |  |  |  |  |  |

| II. | Bac   | ckground                                                                | 7  |  |  |  |  |  |  |  |

|     | 2.1   | Resistive Termination Techniques for <i>LC</i> -Dominant Channels       | 7  |  |  |  |  |  |  |  |

|     |       | 2.1.1 An Intuitive Analytical Channel Model                             | 7  |  |  |  |  |  |  |  |

|     |       | 2.1.2 Resistive Termination Techniques for <i>LC</i> -Dominant Channels | 13 |  |  |  |  |  |  |  |

|     | 2.2   | Feed-Forward Equalization (FFE)                                         |    |  |  |  |  |  |  |  |

|     | 2.3   | Coefficient-Error-Robust FFE (B-FFE)                                    |    |  |  |  |  |  |  |  |

|     | 2.4   | Far-End Crosstalk (FEXT)                                                |    |  |  |  |  |  |  |  |

| Ш   | . Des | sign of a Single-Ended Inverter-based Addition-Only Feed-Forward        |    |  |  |  |  |  |  |  |

|     | Equ   | ualization Transmitter                                                  | 27 |  |  |  |  |  |  |  |

|     | 3.1   | Overview                                                                | 28 |  |  |  |  |  |  |  |

|     | 3.2   | Architecture                                                            | 36 |  |  |  |  |  |  |  |

|     | 3.3   | Robustness to Quantization Errors of Coefficients                       | 45 |  |  |  |  |  |  |  |

|     | 3.4   | Transmitter Design                                                      | 49 |  |  |  |  |  |  |  |

|     | 3.5   | Measurement Results                                                     | 54 |  |  |  |  |  |  |  |

|     | 3.6   | Summary                                                                 | 59 |  |  |  |  |  |  |  |

| IV. | Des   | sign of Compact Single-ended PAM4 Transmitters with Inverter-based      |    |  |  |  |  |  |  |  |

**Crosstalk Compensation for Memory Interfaces**

| Re                  | feren | res                 | 88 |  |  |  |

|---------------------|-------|---------------------|----|--|--|--|

| Summary (in Korean) |       |                     |    |  |  |  |

| V. Conclusion 84    |       |                     |    |  |  |  |

|                     | 4.5   | Summary             | 82 |  |  |  |

|                     | 4.4   | Measurement Results | 75 |  |  |  |

|                     | 4.3   | Transmitter Design  | 68 |  |  |  |

|                     | 4.2   | Architecture        | 66 |  |  |  |

|                     | 4.1   | Overview            | 62 |  |  |  |

# **List of Tables**

| 3.1 | A-FFE Sub-filter Outputs                                           | 38 |

|-----|--------------------------------------------------------------------|----|

| 3.2 | Tap Coefficients of C-FFE and A-FFE for Various Channel Losses     | 38 |

| 3.3 | FFE Output Formulas of C-FFE and A-FFE in terms of FFE Coeffi-     |    |

|     | cients                                                             | 44 |

| 3.4 | Performance Summary and Comparison                                 | 61 |

| 4.1 | Performance Summary and Comparison With Other Reported Transmitter | -  |

|     | side XTC Designs                                                   | 83 |

# **List of Figures**

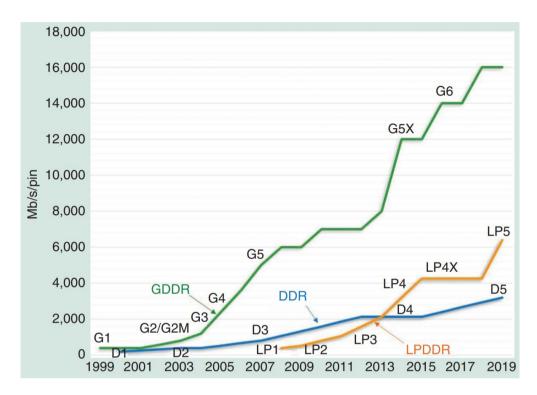

| 1.1 | Data rate trend of DRAM interfaces [1]                                        | 2     |

|-----|-------------------------------------------------------------------------------|-------|

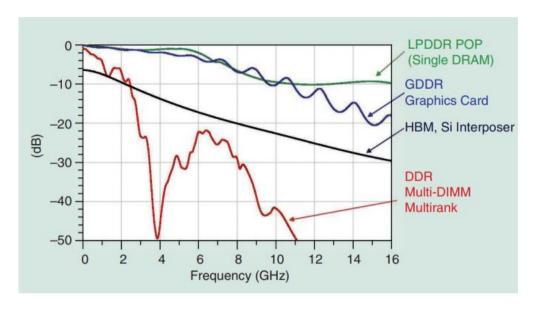

| 1.2 | Channel loss of DRAM interfaces [1]                                           | 3     |

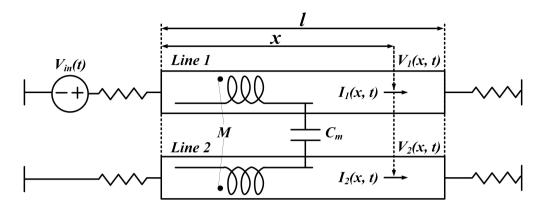

| 2.1 | A schematic diagram of a wireline channel model                               | 8     |

| 2.2 | Intuitive circuit models of wireline channels having (a) voltage-mode         |       |

|     | and (b) current-mode TXs with RXs.                                            | 9     |

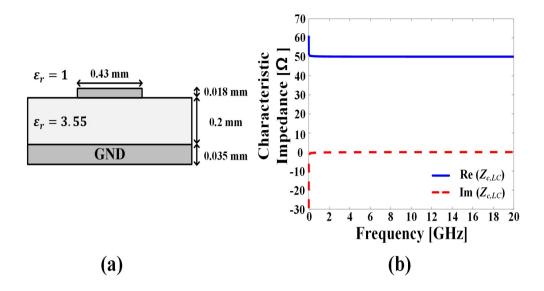

| 2.3 | (a) A cross-sectional view of an example LC-dominant interconnect.            |       |

|     | (b) The simulated characteristic impedance of the LC-dominant inter-          |       |

|     | connect versus the frequency.                                                 | 13    |

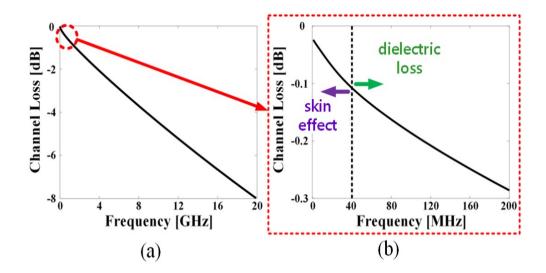

| 2.4 | The simulated $LC$ -dominant channel (Fig. 3(a)) loss versus the fre-         |       |

|     | quency when the channel length is 10 cm. Dominant sources of the              |       |

|     | loss are marked in (b).                                                       | 16    |

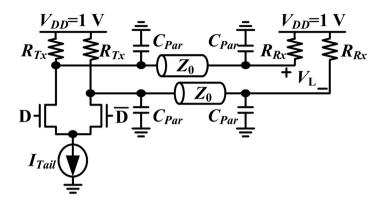

| 2.5 | An example of an interconnect with a CML TX and a voltage-mode                |       |

|     | RX. Parasitic capacitors Cpar are present at the TX output and RX             |       |

|     | input [21]                                                                    | 19    |

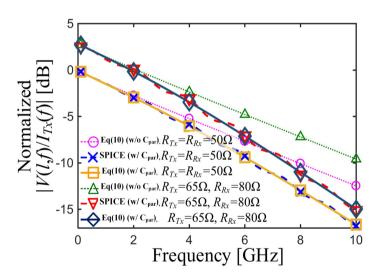

| 2.6 | The magnitude of transfer function $( V_RX(l,f)/I_TX(f) )$ of the in-         |       |

|     | terconnect (Fig. 11) with various $Z0 = 50 \Omega$ , Cpar = 500 fF, and vari- |       |

|     | ous RTX and RRX configuration [21]                                            | 19    |

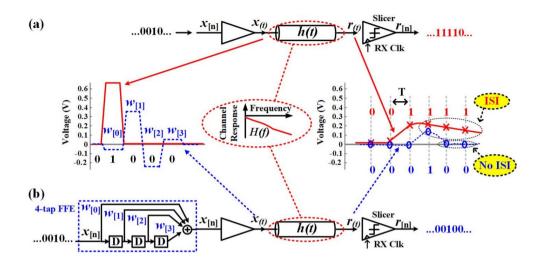

| 2.7 | Comparison of transceiver architectures: (a) conventional transmitter         |       |

|     | without FFE and (b) N-tap FFE transmitter [22]. For a single-bit trans-       |       |

|     | mission case $(x[n] = 1)$ , simulation results show the signal propaga-       |       |

|     | tion through a low-pass channel h(t), from transmitted signal x(t) to         |       |

|     | received signal r(t).                                                         | 20    |

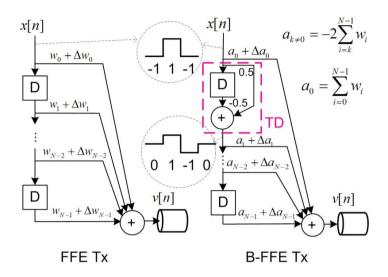

| 2.8 | Block diagrams of an FFE TX and the B-FFE TX [26]                             | 22    |

|     | / :                                                                           | 5. 5. |

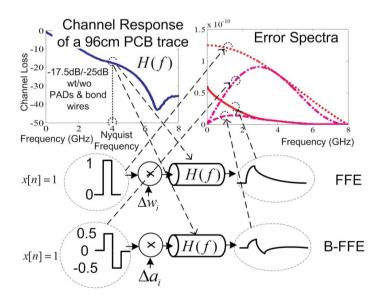

| 2.9  | Error spectra of FFE and B-FFE for one bit pusle [26]                      | 22 |  |  |  |  |  |

|------|----------------------------------------------------------------------------|----|--|--|--|--|--|

| 2.10 | O A schematic diagram of a two-channel model for the FEXT model 2          |    |  |  |  |  |  |

| 3.1  | Comparison of 4-tap TX FFE design options : (a) SST-based C-FFE,           |    |  |  |  |  |  |

| J.1  | (b) an inverter-based C-FFE, and (c) the proposed inverter-based A-        |    |  |  |  |  |  |

|      |                                                                            | 20 |  |  |  |  |  |

| 2.2  | FFE                                                                        | 28 |  |  |  |  |  |

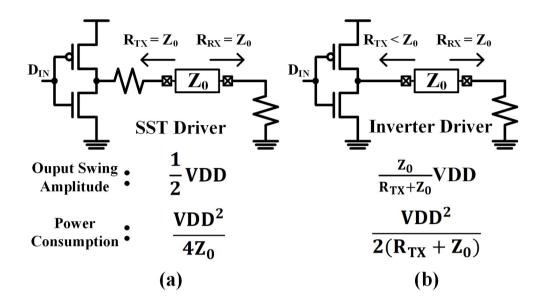

| 3.2  | Schematic of (a) an SST driver and (b) an inverter driver. The output      |    |  |  |  |  |  |

|      | swing amplitudes and average power consumption of the drivers are          |    |  |  |  |  |  |

|      | shown.                                                                     | 30 |  |  |  |  |  |

| 3.3  | The 20 Gb/s eye diagrams of an inverter-based 4-tap C-FFE TX (a)           |    |  |  |  |  |  |

|      | without and (b) with a 20 $\%$ error on the most sensitive tap coefficient |    |  |  |  |  |  |

|      | (the main-cursor). The 20 Gb/s eye diagrams of the inverter-based          |    |  |  |  |  |  |

|      | 4-tap A-FFE TX (c) without and (d) with a 20 % error on the most           |    |  |  |  |  |  |

|      | sensitive tap coefficient (1st post-cursor)                                | 31 |  |  |  |  |  |

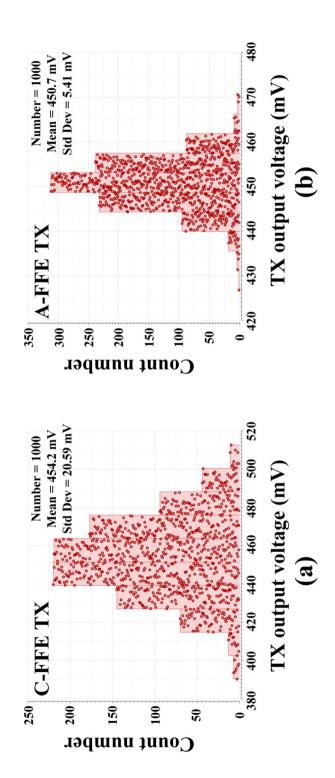

| 3.4  | Output voltage histograms of (a) the inverter-based 4-tap C-FFE TX         |    |  |  |  |  |  |

|      | and (b) the inverter-based 4-tap A-FFE TX when the input data pattern      |    |  |  |  |  |  |

|      | $(D_{pre}, D_{main}, D_{post1}, D_{post2})$ is (-1, -1, -1, -1)            | 32 |  |  |  |  |  |

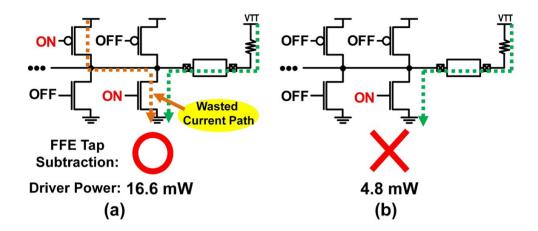

| 3.5  | Current flows of (a) an inverter-based C-FFE TX and (b) the corre-         |    |  |  |  |  |  |

|      | sponding proposed inverter-based A-FFE TX for the same FFE oper-           |    |  |  |  |  |  |

|      | ation. The C-FFE TX is subtracting FFE taps. The average power             |    |  |  |  |  |  |

|      | consumptions of the drivers are also shown                                 | 33 |  |  |  |  |  |

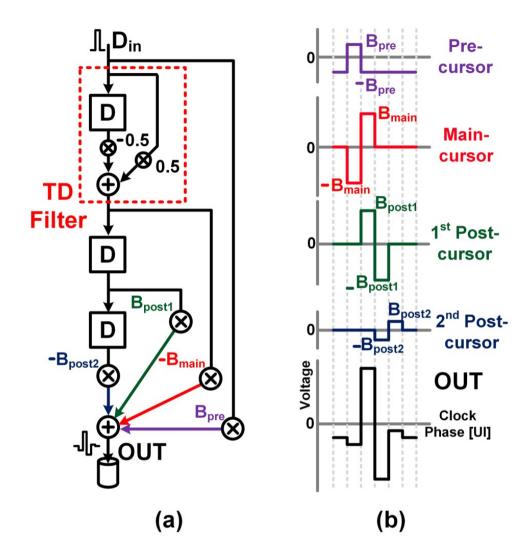

| 3.6  | (a) An example design of the 4-tap B-FFE architecture. (b) The single-     |    |  |  |  |  |  |

|      | bit response and tap driver outputs of the 4-tap B-FFE example             | 35 |  |  |  |  |  |

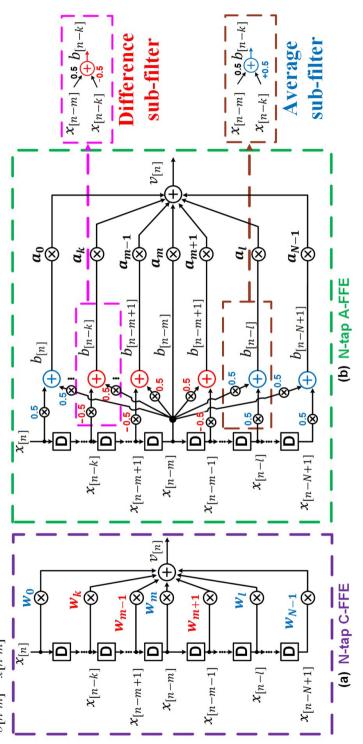

| 3.7  | Block diagrams of (a) an N-tap C-FFE TX and (b) an N-tap A-FFE TX.         | 37 |  |  |  |  |  |

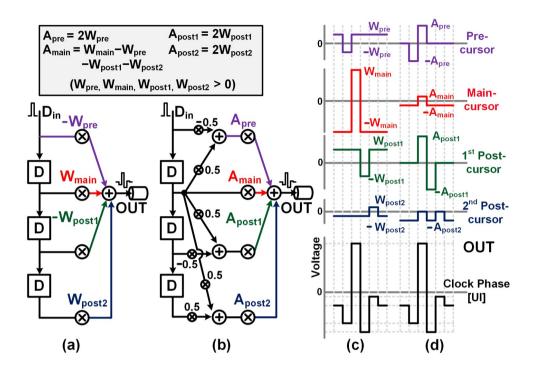

| 3.8  | Example designs of the identical 4-tap FFE employing (a) C-FFE and         |    |  |  |  |  |  |

|      | (b) A-FFE architectures. The single-bit responses and tap driver out-      |    |  |  |  |  |  |

|      | puts of (c) the C-FFE and (d) the A-FFE examples                           | 42 |  |  |  |  |  |

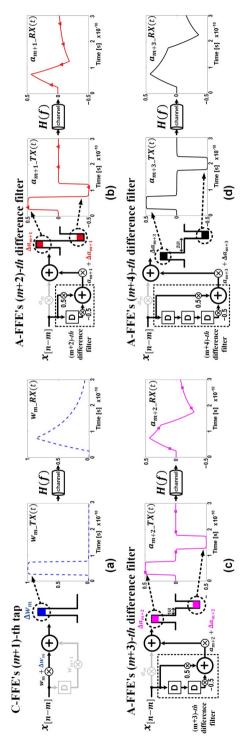

| 3.9  | Error signals when C-FFE and A-FFE TXs transmit a single bit pulse       |      |

|------|--------------------------------------------------------------------------|------|

|      | at 20 Gb/s and there are 20 % quantization errors on (a) (m+1)-th C-     |      |

|      | FFE tap coefficient, (b) (m+2)-th A-FFE tap coefficient, (c) (m+3)-th    |      |

|      | A-FFE tap coefficient, and (d) (m+4)-th A-FFE tap coefficient. A 1st-    |      |

|      | order RC channel with a loss of 15 dB at Nyquist frequency and a time    |      |

|      | constant of 88 ps is employed for the simulations                        | 46   |

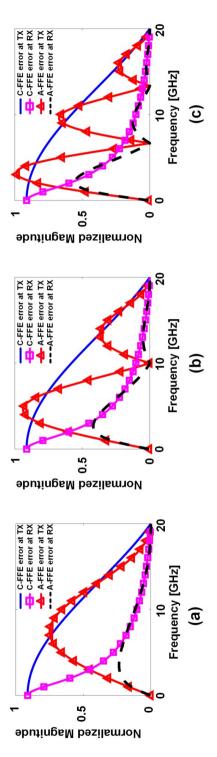

| 3.10 | The frequency-domain transmitted and received error signals of the       |      |

|      | C-FFE and the A-FFE caused (a) by 20 % quantization errors on the        |      |

|      | (m+1)-th C-FFE tap coefficient and (m+2)-th A-FFE tap coefficient,       |      |

|      | (b) by 20 % quantization errors on the (m+1)-th C-FFE tap coefficient    |      |

|      | and (m+3)-th A-FFE tap coefficient, (c) by 20 % quantization errors      |      |

|      | on the (m+1)-th C-FFE tap coefficient and (m+4)-th A-FFE tap coef-       |      |

|      | ficient, respectively.                                                   | 48   |

| 3.11 | A schematic diagram of the implemented 4-tap A-FFE TX                    | 50   |

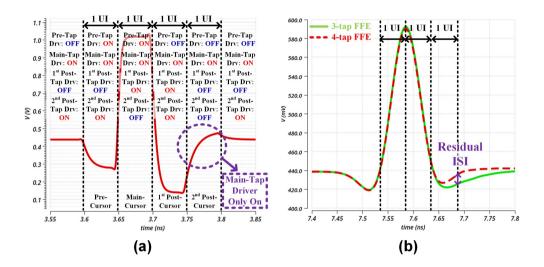

| 3.12 | (a) The single-bit responses of the 4-tap A-FFE at TX output. (b) The    |      |

|      | single-bit responses of the 4-tap and 3-tap A-FFE at RX input            | 51   |

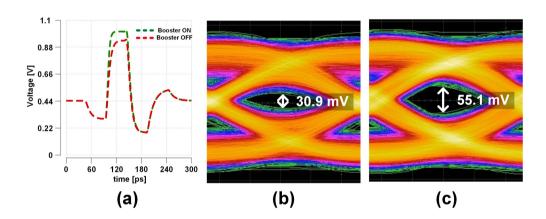

| 3.13 | Simulated and measured TX outputs with and without enabling a booster    |      |

|      | tap driver at 20 Gb/s with 1.1 V supply: (a) a simulated one bit pulse   |      |

|      | response, (b) a measured eye diagram with a disabled booster tap         |      |

|      | driver, (c) a measured eye diagram with a enabled booster tap driver     | 51   |

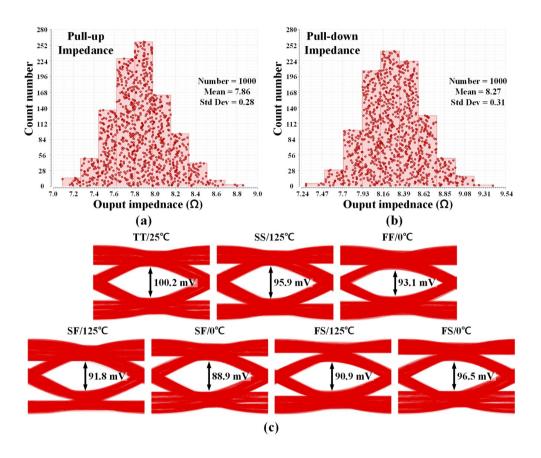

| 3.14 | Histograms of the A-FFE TX's output impedance and simulated eye          |      |

|      | diagrams of TX output across corners: (a) the pull-up impedance, (b)     |      |

|      | the pull-down impedance, and (c) simulated eye diagrams                  | 53   |

| 3.15 | A schematic diagram of clocking circuits for serializing 2:1 MUXs        | 54   |

| 3.16 | A die micrograph.                                                        | 56   |

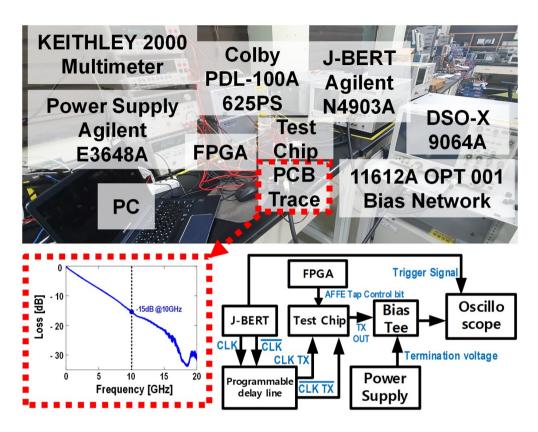

| 3.17 | The test setup.                                                          | 57   |

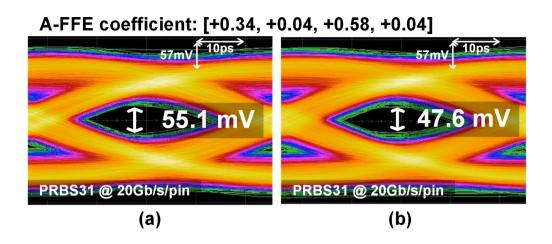

| 3.18 | Measured eye diagrams of the 4-tap A-FFE TX: (a) without and (b)         |      |

|      | with a 20 $\%$ error on the most sensitive tap (1st pre-tap) coefficient | 58   |

|      |                                                                          |      |

|      | VIII (S)                                                                 |      |

|      | – VIII –                                                                 |      |

|      | ection @ postech                                                         |      |

| COII | color w pooleon                                                          | 4.84 |

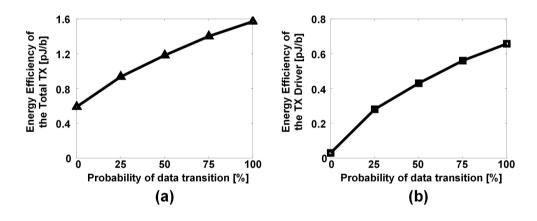

| The measured A-FFE TX energy consumption versus probability of          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| data transition: the energy consumption of (a) the total TX circuit and |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| (b) the only drivers                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

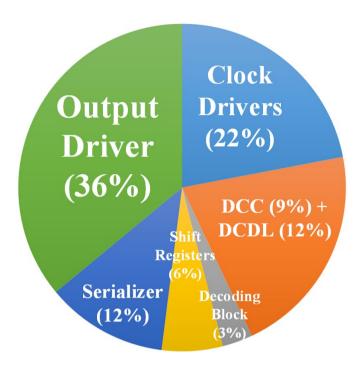

| The power breakdown of the A-FFE TX                                     | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

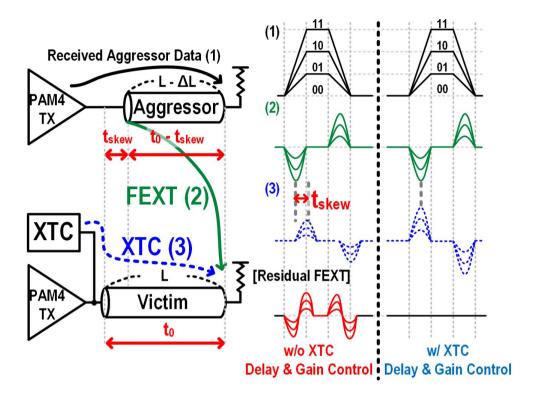

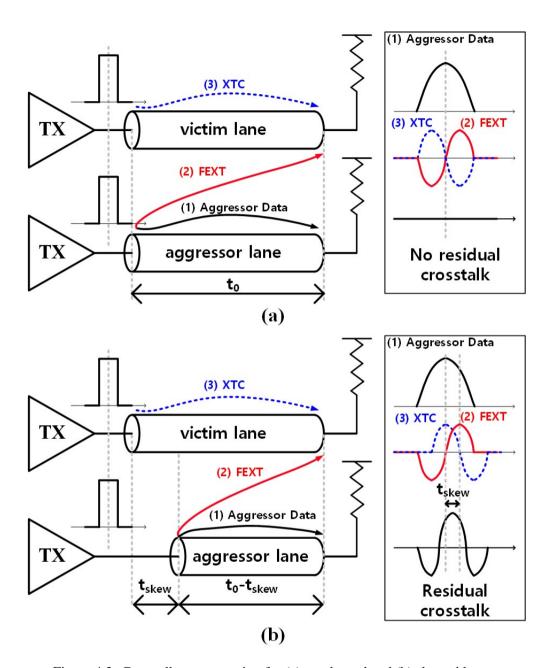

| PAM4 crosstalk compensation                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Crosstalk compensation for (a) un-skewed and (b) skewed lanes           | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

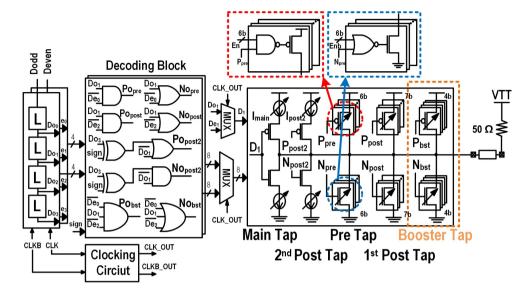

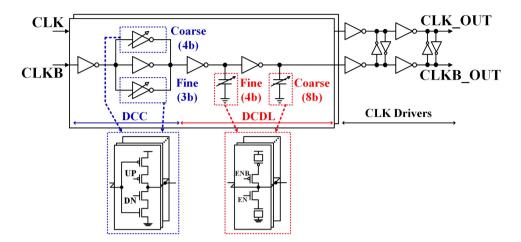

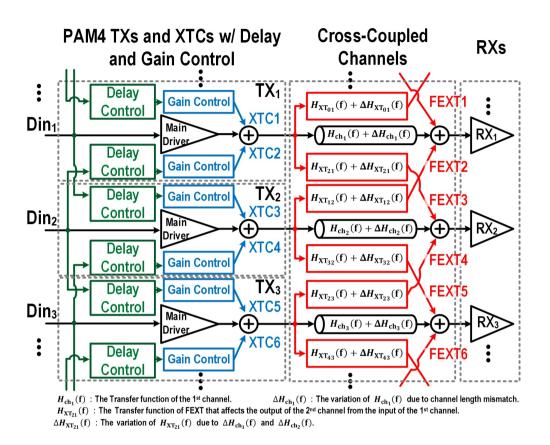

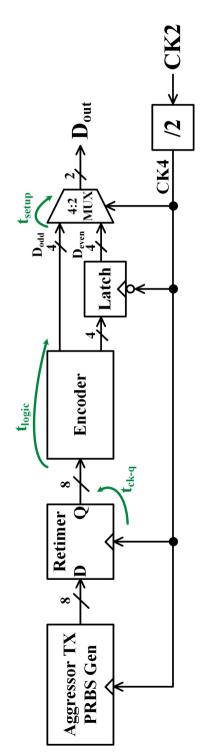

| The overall architecture of the proposed TX                             | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

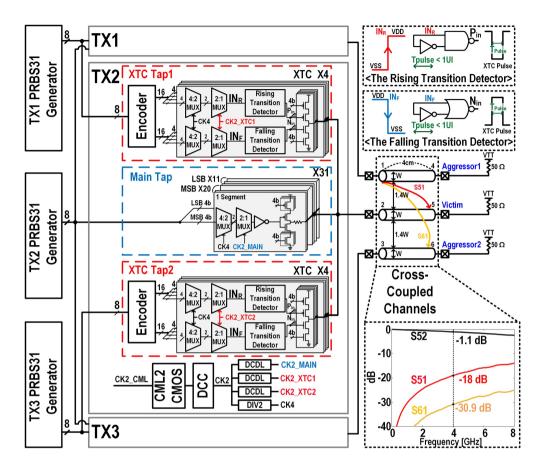

| The schematic diagram of the transmitter and the S-parameters of the    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| interconnects                                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| A schematic diagram of the 4:2 MUX with the encoder for XTC seg-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ments                                                                   | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Encoding table for XTC segments, and the Boolean expressions of the     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| encoded input (INR, INF) to the four XTC segments (SEG1, SEG2,          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| SEG3, and SEG4)                                                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

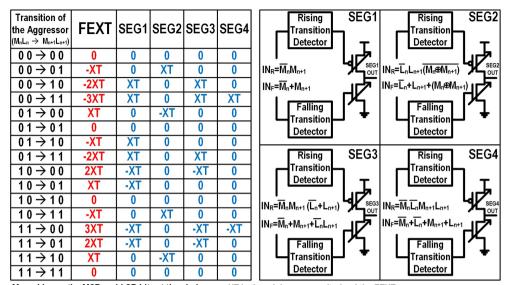

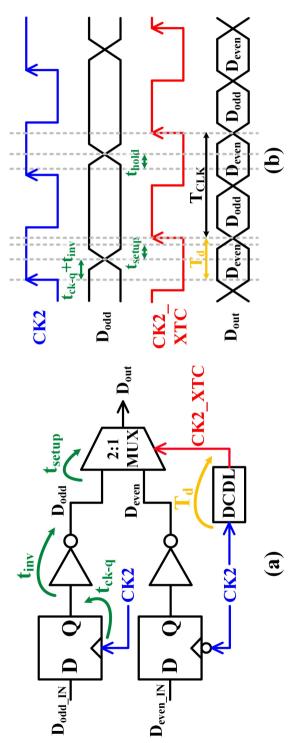

| (a) A schematic diagram of the DCDL and (b) delay increments of the     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| DCDL versus fine and coarse digital codes under different corners and   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| temperatures                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

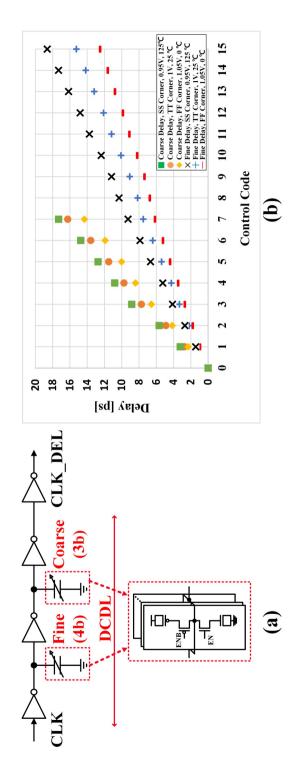

| (a) Retimer and 2-to-1 MUX. (b) 2-to-1 MUX timing                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

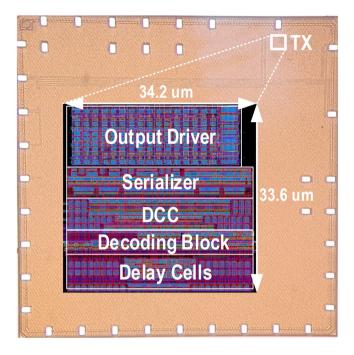

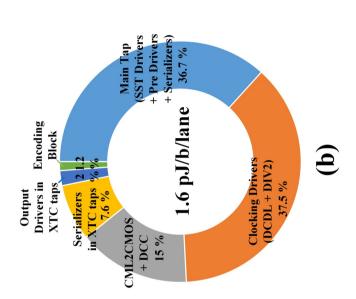

| (a) A chip microphotograph and (b) the power breakdown of the pro-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| posed PAM4 TX with XTC taps                                             | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

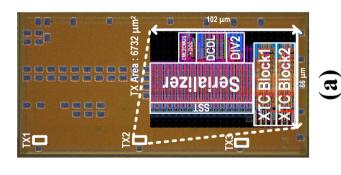

| A measurement setup.                                                    | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

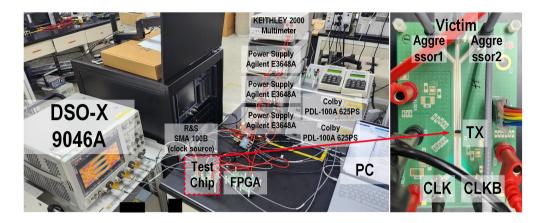

| A measured FEXT eye diagram when two TXs at the aggressor chan-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| nels generate 16 Gb/s PAM4 signals.                                     | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

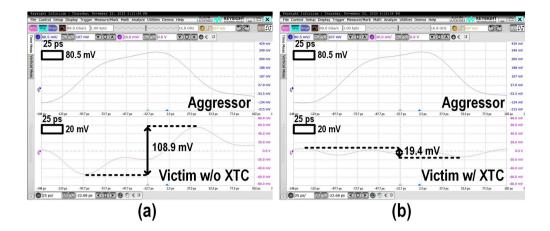

| Measured single-bit responses at the aggressor and FEXT pulses at the   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| victim (a) without and (b) with XTC.                                    | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Measured PAM4 TX eye diagrams with and without XTC taps, delay          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| control, and aggressors.                                                | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

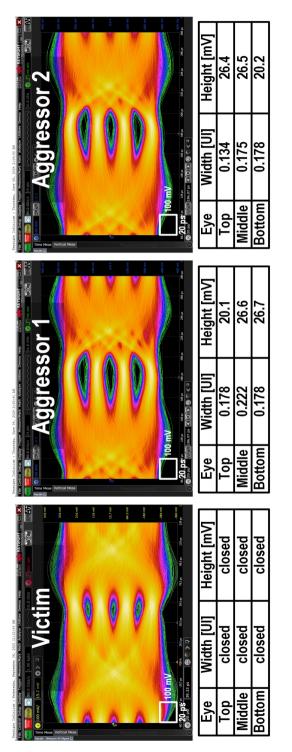

|                                                                         | data transition: the energy consumption of (a) the total TX circuit and (b) the only drivers.  The power breakdown of the A-FFE TX.  PAM4 crosstalk compensation.  Crosstalk compensation for (a) un-skewed and (b) skewed lanes.  The overall architecture of the proposed TX.  The schematic diagram of the transmitter and the S-parameters of the interconnects.  A schematic diagram of the 4:2 MUX with the encoder for XTC segments.  Encoding table for XTC segments, and the Boolean expressions of the encoded input (INR, INF) to the four XTC segments (SEG1, SEG2, SEG3, and SEG4).  (a) A schematic diagram of the DCDL and (b) delay increments of the DCDL versus fine and coarse digital codes under different corners and temperatures.  (a) Retimer and 2-to-1 MUX. (b) 2-to-1 MUX timing.  (a) A chip microphotograph and (b) the power breakdown of the proposed PAM4 TX with XTC taps.  A measurement setup.  A measured FEXT eye diagram when two TXs at the aggressor channels generate 16 Gb/s PAM4 signals.  Measured single-bit responses at the aggressor and FEXT pulses at the victim (a) without and (b) with XTC.  Measured PAM4 TX eye diagrams with and without XTC taps, delay |  |  |  |  |  |

| 4.14 | Measured PAM4    | ГХ еуе  | diagrams   | of the | victim | and | two | aggre | ssors |    |

|------|------------------|---------|------------|--------|--------|-----|-----|-------|-------|----|

|      | without XTC taps | and del | ay control |        |        |     |     |       |       | 81 |

## I. Introduction

The increasing demand for high-performance memory interfaces has been driven by the growth of computing technologies and data-intensive applications. Developments in areas such as artificial intelligence, machine learning, and multimedia require memory interfaces that offer high speed, low latency, and energy efficiency. Single-ended interfaces have been widely adopted in modern memory systems like Graphic Double Data Rate (GDDR) memory and High Bandwidth Memory (HBM) due to their high pin efficiency, area efficiency, and low power consumption [1].

As illustrated in Fig. 1.1, the required data rates for dynamic random-access memory (DRAM) interfaces have been rising and are expected to surpass 16 Gb/s, particularly for GDDR modules. This increase has led to greater channel losses, exceeding -10 dB as shown in Fig. 1.2. Such losses amplify the effects of inter-symbol interference (ISI), further reducing the sampling margin. To mitigate these challenges, transmitter (TX) equalizers like feed-forward equalizers (FFE) are commonly employed in memory interfaces [2], [3], [4].

Designing high-speed memory interfaces presents two main challenges. First, overcoming the bandwidth limitations of transmission channels necessitates effective equalization techniques. Second, maintaining signal integrity becomes more difficult due to increasing crosstalk interference in parallel interfaces. Traditional approaches to these issues often involve trade-offs among performance, power consumption, and area efficiency.

#### 1.1 Motivation

As data rates surpass tens of gigabits per second, TX architectures encounter significant challenges in maintaining signal integrity while adhering to power and area

Figure 1.1: Data rate trend of DRAM interfaces [1].

constraints. Traditional high-speed TX designs often utilize source-series terminated (SST) drivers because of their linearity and impedance matching properties. However, SST drivers have limitations in modern memory interfaces. The considerable area consumed by termination resistors and the parasitic capacitance inherent in SST drivers negatively impact the output bandwidth at higher data rates, diminishing their effectiveness in advanced applications.

Inverter-based drivers offer an alternative approach for memory interfaces, providing advantages in area efficiency and power consumption [5]. Their compact design is particularly beneficial for memory systems that require numerous I/O channels within a limited silicon area. The simpler circuit structure of inverter-based drivers also results in reduced parasitic capacitance. Despite these benefits, implementing ef-

Figure 1.2: Channel loss of DRAM interfaces [1].

fective equalization techniques with inverter-based drivers poses technical challenges, especially in terms of maintaining linearity and controlling output impedance [3], [4].

To achieve higher data rates without increasing channel bandwidth, four-level pulse-amplitude modulation (PAM4) signaling has been adopted in memory interfaces. PAM4 transmits two bits per symbol by employing four voltage levels, effectively doubling the data rate compared to binary signaling. This makes PAM4 suitable for applications where bandwidth limitations are a primary concern. However, the multilevel nature of PAM4 introduces additional design considerations, such as reduced voltage margins and increased sensitivity to noise.

In short-reach memory interfaces, crosstalk noise has become a more significant issue than channel loss-induced ISI. Due to the short channel lengths in memory modules, far-end crosstalk (FEXT) emerges as the main source of signal degradation [6]. This problem is exacerbated in PAM4 systems, where the eye height is one-third of that in binary signaling. The reduced voltage margins between PAM4 levels increase the system's sensitivity to crosstalk interference, necessitating effective compensation

SCIENCEAND

## 1.2 Application and Problem Overview

High-speed memory interfaces face specific challenges in implementing signaling techniques. The requirement for area efficiency in parallel I/O channels, combined with the need to maintain signal integrity at higher data rates, imposes significant design constraints. Traditional inverter-based FFE implementations involve tap subtraction operations, which add complexity and can affect reliability, particularly when precise coefficient control is needed to sustain signal quality [3], [4].

Implementing PAM4 signaling introduces additional considerations for signal integrity management. The varying crosstalk patterns associated with different PAM4 voltage level combinations necessitate more sophisticated cancellation techniques [6]. Current approaches to crosstalk cancellation often employ complex circuits that consume considerable area and power, presenting challenges for integration into dense memory interfaces.

Designing efficient TXs requires careful balancing of signal integrity, power consumption, and area efficiency. While inverter-based architectures offer promising solutions to meet these requirements, new methods are needed to overcome traditional limitations in equalization and signal conditioning applications.

#### 1.3 Thesis Contributions

This thesis introduces two TX architectures that address challenges in high-speed memory interfaces: an addition-only feed-forward equalizing (A-FFE) TX and a PAM4 TX with crosstalk compensation (XTC). Both architectures focus on achieving compact and energy-efficient designs using inverter-based implementations.

The first contribution is a 4-tap A-FFE TX designed for single-ended interfaces.

Unlike conventional FFE TXs that use SST drivers with area-consuming linear resis

tors and high parasitic capacitance, the proposed A-FFE architecture eliminates tap subtraction operations. This simplification enhances robustness to coefficient quantization errors and reduces circuit complexity. Implemented in 28-nm LP CMOS technology, the prototype operates at 20 Gb/s per pin and achieves an eye height of 55.1 mV and an eye width of 0.44 unit interval (UI) over a 15 dB printed circuit board (PCB) trace. The design demonstrates a power efficiency of 1.18 pJ per bit and shows a 68 % worst-case eye sensitivity, with only a 13.6 % reduction in eye opening when the most sensitive FFE coefficient is decreased by 20 %. The inverter-based, resistor-free design occupies a compact area of 1,149 µm<sup>2</sup>.

The second contribution is a PAM4 TX with crosstalk compensation tailored for short-reach memory interfaces. The design includes efficient encoders and transition detectors for crosstalk pattern recognition, along with inverter-based XTC tap control. The architecture features precise gain and delay control mechanisms to minimize compensation errors between victim and aggressor channels. Fabricated in 28-nm LP CMOS technology, the TX operates at 16 Gb/s and demonstrates improvements in eye height and width by 203 % and 396 %, respectively, when crosstalk compensation is enabled. The area-efficient design occupies 0.0067 mm², achieving an area per data rate of 0.00042 mm²/Gbps.

These architectures provide practical solutions for implementing high-speed memory interfaces, emphasizing area and power efficiency through inverter-based designs.

## 1.4 Thesis Organization

The rest of this thesis is organized as follows:

Chapter 2 provides a theoretical background on wireline channel behavior and FFE techniques used for ISI compensation in high-speed transmitters. It reviews the limitations of conventional FFE (C-FFE) transmitters, particularly those employing SST drivers with linear resistors. The chapter also discusses prior work on relaxed impedance matching techniques and coefficient-error-robust FFE (B-FFE) architec-

tures. Additionally, it presents a theoretical analysis of FEXT in high-speed memory interfaces, which is crucial for understanding the challenges addressed in later chapters.

Chapter 3 introduces the design and implementation of the addition-only feed-forward equalizing (A-FFE) transmitter architecture. This chapter explains how eliminating subtractions between FFE taps enhances robustness to coefficient quantization errors and enables the use of area- and power-efficient inverter-based drivers. The inverter-based 4-tap A-FFE transmitter is detailed, including its circuit design, implementation in 28-nm LP CMOS technology, and performance evaluation. Experimental results demonstrate the transmitter's ability to achieve 20 Gb/s per pin with improved power efficiency and a compact area.

Chapter 4 presents a PAM4 transmitter with crosstalk compensation (XTC) for short-reach memory interfaces. The chapter outlines the challenges of implementing PAM4 signaling in the presence of crosstalk and describes the proposed solution using inverter-based XTC taps. It covers the design of efficient encoders and transition detectors for crosstalk pattern recognition, as well as mechanisms for precise gain and delay control to minimize compensation errors between victim and aggressor channels. Measurement results from the 28-nm LP CMOS prototype demonstrate significant improvements in signal integrity with the XTC enabled.

Chapter 5 summarizes the contributions of the thesis and provides concluding remarks. It reflects on how the proposed inverter-based transmitter architectures address the challenges in high-speed memory interfaces and suggests potential directions for future research in this area.

This dissertation is based on the papers published in *IEEE Journal of Solid-State Circuits* [4] and *IEEE Transactions on Circuits and Systems II: Express Briefs* [6]. The material has been reused in accordance with the *IEEE* reuse policy, and proper credit has been given to the original sources as follows: *Copyright* © 2024, *IEEE*.

# II. Background

# 2.1 Resistive Termination Techniques for *LC*-Dominant Channels

Resistive termination with 50- $\Omega$  resistors is a trivial impedance matching method widely used in conventional standard 50- $\Omega$  applications. However, the simple 50- $\Omega$  matching too strictly constrains the transceiver (TRX) design, preventing design improvement beyond the 50- $\Omega$  matching constraint. Because the design challenges have been significantly increased after decades of advancements in wireline technology, the potential room for further improvement beyond the traditional 50- $\Omega$  matching constraint is increasingly attractive.

In LC-dominant applications, by carefully changing the channel behavior, the non-conventional design choice of resistive termination improves the link performance such as eye height or power efficiency beyond the impedance matching constraint.

We review several design techniques of resistive termination from the perspectives of channel behaviors.

## 2.1.1 An Intuitive Analytical Channel Model

In this section, we explain an intuitive analytical channel model in the frequency domain that helps designers easily understand various trade-offs by resistive termination so that the designer can appropriately design the resistive termination considering the channel behavior and the overall link performance.

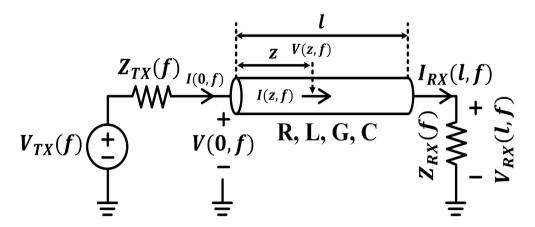

Figure 2.1: A schematic diagram of a wireline channel model.

#### 2.1.1.1 An Approximate Transfer Function Model

A wireline channel is typically modeled as a transmission line (TL) having a transmitter (TX) and a receiver (RX) (Fig. 2.1). The TX is modeled as a Thévenin-equivalent circuit having a voltage source  $V_{TX}(f)$  and an impedance  $Z_{TX}(f)$ . The RX is modeled as an input impedance  $Z_{RX}(f)$ . The interconnect of length l is modeled with RLGC parameters, where R, L, G, and G denote the per-unit-length resistance, inductance, conductance, and capacitance, respectively. V(z, f) and I(z, f) are the voltage and the current along the channel at a distance z from the TX, respectively (Fig. 2.1). The channel's rigorous transfer function (2.4) can be derived by solving the telegrapher's equation (2.1), with boundary conditions (2.2) and (2.3) [9].

$$-\frac{\partial}{\partial z} \begin{bmatrix} V(z,f) \\ I(z,f) \end{bmatrix} = \begin{bmatrix} 0 & R+j2\pi fL \\ G+j2\pi fC & 0 \end{bmatrix} \begin{bmatrix} V(z,f) \\ I(z,f) \end{bmatrix}$$

(2.1)

$$V_{TX}(f) = V(0, f) + I(0, f)Z_{TX}(f)$$

(2.2)

$$V_{RX}(l,f) = I_{RX}(l,f)Z_{RX}(f).$$

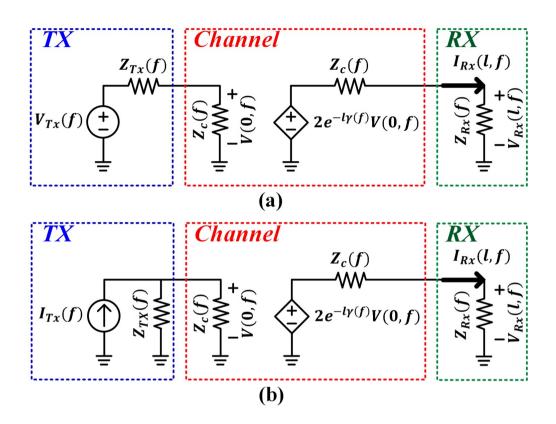

Figure 2.2: Intuitive circuit models of wireline channels having (a) voltage-mode and (b) current-mode TXs with RXs.

$$\frac{V_{RX}(l,f)}{V_{TX}(f)} = Z_C(f)Z_{RX}(f)/[(Z_C(f)^2 + Z_{TX}(f)Z_{RX}(f))\sinh(\gamma(f)l)

+ (Z_C(f)Z_{TX}(f) + Z_C(f)Z_{RX}(f))\cosh(\gamma(f)l)], \quad (2.4)$$

where  $Z_C(f)$  and  $\gamma(f)$  are the characteristic impedance and propagation constant of the interconnect, respectively.

$$Z_C(f) = \sqrt{\frac{R + j2\pi fL}{G + j2\pi fC}}$$

$$\gamma(f) = \sqrt{(R + j2\pi f L)(G + j2\pi f C)} \tag{2.6}$$

Although the formula (2.4) is rigorously derived without approximation, it is too complex to provide design intuition. Instead, equation (2.4) can be rewritten into the same but more intuitive formula (2.7).

$$\frac{V_{RX}(l,f)}{V_{TX}(f)} = \frac{Z_C(f)}{Z_{TX}(f) + Z_C(f)} 2e^{-l\gamma(f)} \frac{Z_{RX}(f)}{Z_C(f) + Z_{RX}(f)} \frac{1}{1 - \eta(f)},$$

(2.7)

where  $\eta(f) = \Gamma_{TX}(f)\Gamma_{RX}(f)e^{-2l\gamma(f)}$ ,  $\Gamma_{TX}(f) = (Z_{TX}(f) - Z_C(f))/(Z_{TX}(f) + Z_C(f))$ , and  $\Gamma_{RX}(f) = (Z_{RX}(f) - Z_C(f))/(Z_{RX}(f) + Z_C(f))$ .  $\Gamma_{TX}(f)$  and  $\Gamma_{RX}(f)$  are the reflection coefficients at the TX and the RX, respectively.  $\eta(f)$  is the round-trip gain of a reflected wave traveling back and forth between the TX and the RX.

The term  $1/(1-\eta(f))$  in (2.7) complicates the channel behavior if  $\eta(f) \neq 0$ . A complex channel behavior is not preferred in wireline applications because it requires complex hardware to implement broadband signaling. For this reason, resistive terminations are usually designed to simplify the channel behavior for a broad frequency range. Because  $|\eta(f)|$  is the product of three terms  $|\Gamma_{TX}(f)|$ ,  $|\Gamma_{RX}(f)|$ , and  $|e^{-2l\gamma(f)}|$ , all of which are usually smaller than 1, designers can easily make  $|\eta(f)| \ll 1$  in most practical designs, where reflection is avoided. For instance, if  $|\Gamma_{TX}(f)| = 0.5$ ,  $|\Gamma_{RX}(f)| = 0.5$ , and  $|e^{-2l\gamma(f)}| = 0.5$ , then  $|\eta(f)| = 0.0625 \ll 1$  even though the reflection coefficients are large: this condition  $(|\eta(f)| \ll 1)$  is traditionally enforced by impedance matching  $(|\Gamma_{TX}(f)| = |\Gamma_{RX}(f)| = 0)$ . Therefore, we may assume (2.8), and approximate (2.7) to (2.9), an intuitive closed-form transfer function of a wireline channel:

$$|\eta(f)| = |\Gamma_{TX}(f)\Gamma_{RX}(f)e^{-2\gamma(f)}| \ll 1,$$

$$\frac{V_{RX}(l,f)}{V_{TX}(f)} \approx \frac{Z_C(f)}{Z_{TX}(f) + Z_C(f)} 2e^{-l\gamma(f)} \frac{Z_{RX}(f)}{Z_C(f) + Z_{RX}(f)},$$

(2.9)

Equation (2.9) accurately describes the transfer function if the validity condition (2.8) is satisfied [2].

The approximate transfer function (2.9) can be intuitively modeled using an equivalent voltage-controlled voltage source (VCVS) model of a transmission line (Fig. 2.2). The circuit model of the channel in Fig. 2.2(a) is obtained by replacing the transmission line in Fig. 2.1 with the equivalent VCVS model, which has input and output impedances of  $Z_C(f)$  and a gain of  $2e^{-l\gamma(f)}$ .  $Z_C(f)$  is the characteristic impedance (2.5), and the channel's length l is included in the VCVS gain  $2e^{-l\gamma(f)}$ .

If the current-mode TX or the current-model RX is used, the model can be easily modified. The current-mode TX can be modeled with a Norton-equivalent current source  $I_{TX}(f)$  with an impedance  $Z_{TX}(f)$  (Fig. 2.2(b)) instead of a Thévenin-equivalent circuit of the voltage-mode TX in Fig. 2.2(a). If the current-mode RX is used instead of the voltage-mode RX, the input current into the same RX impedance  $Z_{RX}(f)$  can be used as the received signal instead of the voltage across  $Z_{RX}(f)$  (Fig. 2.2).

The transfer function  $V_{RX}(l,f)/I_{TX}(l,f)$  of the channel with a current-mode TX and a voltage-mode RX is

$$\frac{V_{RX}(l,f)}{I_{TX}(f)} \approx \frac{Z_{TX}(f)Z_C(f)}{Z_{TX}(f) + Z_C(f)} 2e^{-l\gamma(f)} \frac{Z_{RX}(f)}{Z_C(f) + Z_{RX}(f)}$$

(2.10)

With a voltage-mode TX and a current-mode RX, the transfer function  $I_{RX}(l,f)/V_{TX}(l,f)$  is

$$\frac{I_{RX}(l,f)}{V_{TX}(f)} \approx \frac{Z_C(f)}{Z_{TX}(f) + Z_C(f)} 2e^{-l\gamma(f)} \frac{1}{Z_C(f) + Z_{RX}(f)}$$

(2.11)

With a current-mode TX and a current-mode RX, the transfer function  $I_{RX}(l,f)/I_{TX}(l,f)$  is

$$\frac{I_{RX}(l,f)}{I_{TX}(f)} \approx \frac{Z_{TX}(f)Z_C(f)}{Z_{TX}(f) + Z_C(f)} 2e^{-l\gamma(f)} \frac{1}{Z_C(f) + Z_{RX}(f)}$$

(2.12)

The transfer functions (2.9)-(2.12) can be easily extended even if the TX and the RX impedances are not resistive and have extra parasitic components [10]. Equation (2.9)-(2.12) holds even though the TX and RX impedances are not resistive. If there are parasitic capacitors or inductors at the TX and RX, then the parasitic elements can be added to the circuit model (Fig. 2.2) while the validity condition (2.8) must be appropriately modified by using Thévenin's and Norton's Theorems [10].

#### 2.1.1.2 Design Intuition for Termination Impedances

The channel models provide two simple, intuitive, separate formulas to understand how the TX and the RX impedance affect the channel behavior. In equation (2.9), the transfer function can be interpreted as a product of the three terms: 1) the voltage division between the TX impedance and the channel's characteristic impedance  $Z_C(f)/(Z_{TX}(f)+Z_C(f))$ ; 2) the interconnect's attenuation  $(2e^{-l\gamma(f)})$  modeled by a VCVS; and 3) the voltage division between the channel's characteristic impedance and the RX impedance  $Z_{RX}(f)/(Z_C(f)+Z_{RX}(f))$  (Fig. 2.2).

Because this transfer function model has three separate terms for the TX, the interconnect, and the RX, this formula provides a clear intuition of how each of these components affects the channel behavior. The impedance  $Z_{TX}(f)$  of the TX appears only in the first voltage division term at the TX, whereas the RX impedance  $Z_{RX}(f)$  appears only in the third voltage division term at the RX. The length l of the interconnect and the propagation constant  $\gamma(f)$  only appear in the second interconnect's attenuation term.

Therefore, during the TX impedance design, a designer can only focus on the  $Z_C(f)/(Z_{TX}(f)+Z_C(f))$  term in order to consider the channel behavior affected by the  $Z_{TX}(f)$  without considering the other two terms that are independent of  $Z_C(f)$ . Similarly, when designing the RX impedance, the designer can only focus on the

Figure 2.3: (a) A cross-sectional view of an example *LC*-dominant interconnect. (b) The simulated characteristic impedance of the *LC*-dominant interconnect versus the frequency.

$Z_{RX}(f)/(Z_C(f)+Z_{RX}(f))$  term without considering the other two terms. Therefore, if the validity condition (2.8) is satisfied, we can interpret these terms as the interconnect-TX and interconnect-RX interaction terms, respectively. A similar discussion holds for the other three transfer function cases (2.10)-(2.12).

#### 2.1.2 Resistive Termination Techniques for *LC*-Dominant Channels

In this section, we review several resistive termination techniques from the perspective of *LC*-dominant channel behaviors in the frequency domain. Firstly, we explain the characteristics of an *LC*-dominant channel using the intuitive model explained in Section 2.1.1, and then we review several resistive termination techniques, especially, emphasizing the relaxed impedance matching technique that enables a design beyond the limitation of the impedance matching constraint.

#### 2.1.2.1 Characteristics of *LC*-Dominant Channels

Typical interconnects are LC-dominant channels. Ideally, they do not suffer from channel losses because the resistance R and conductance G parameters are negligible in their ideal RLGC model. However, in reality, skin effect and dielectric loss cause significant channel loss.

Skin effect is a phenomenon that the current concentrates on the conductor's surface at high frequencies because of the induced magnetic field in the conductor. This effect slows phase velocity and increases series impedance and attenuation. Skin depth  $\delta_s$  is the distance where current density decreases by  $e^{-1}$ , and can be expressed as

$$\delta_s = \sqrt{\frac{\rho}{\pi f \mu}} \tag{2.13}$$

where  $\rho$ ,  $\mu$ , and f are the electrical resistivity, permeability, and the frequency, respectively [11], [12], [13]. The surface impedance  $Z_s$  is given by:

$$Z_s = \sqrt{\pi f \mu \rho (1+j)} = R_s \sqrt{f(1+j)}$$

(2.14)

where  $R_s = \sqrt{\pi\mu\rho}$  is the skin effect parameter [12], [13].

Dielectric loss refers to the energy dissipation within the dielectric material of the transmission lines. This loss is primarily characterized by the loss tangent  $\delta_d$ , which is a ratio of the material's energy loss to the energy stored within it. The loss tangent is the ratio of the imaginary part to the real part of the dielectric constant [11], [12]. Materials with higher loss tangents will experience greater dielectric losses, leading to increased signal attenuation and reduced transmission efficiency. The dielectric loss parameter  $G_d$  is given by:

$$G_d = 2\pi C \tan \delta_d \tag{2.15}$$

where C is the per-unit-length capacitance [11].

To model the skin effect and dielectric loss, the  $R+j2\pi fL$  and  $G+j2\pi fC$  terms in (1) are modified as

$$R + j2\pi f L = R_0 + R_s \sqrt{f} + j(2\pi f L + R_s \sqrt{f})$$

(2.16)

$$G + j2\pi fC = G_0 + fG_d + j2\pi fC. \tag{2.17}$$

$R_0$  and  $G_0$  are the static resistance and the conductance parameters, respectively.

In LC-dominant channels, the inductance L and capacitance C parameters are dominant in the transmission line while  $R_0$  and  $G_0$  are negligible [14]:

$$2\pi f L \gg R_s \sqrt{f} \gg R_0, \quad 2\pi f C \gg G_d f \gg G_0.$$

(2.18)

With conditions (2.18), (2.16) can be simplified to (2.19).

$$R + j2\pi fL \approx R_0 + R_s \sqrt{f} + j2\pi fL \tag{2.19}$$

With (2.18) and (2.19), the characteristic impedance (2.20) and propagation constant (2.21) of an LC-dominant channel can be derived [14]:

$$Z_{C,LC}(f) \approx Z_0 = \sqrt{L/C}, \tag{2.20}$$

$$\gamma_{LC}(f) \approx j2\pi\sqrt{LC}f + \frac{R_s}{2Z_{C,LC}}\sqrt{f} + \frac{G_dZ_{C,LC}}{2}f. \tag{2.21}$$

Even with skin effect and dielectric loss, the characteristic impedance  $Z_{C,LC}(f)$  of an LC-dominant interconnect is almost the same constant resistance as the characteristic impedance  $Z_0 = \sqrt{L/C}$  of the ideal transmission line (2.20). In a 2-D field solver simulation of an example LC-dominant microstrip line (Fig. 2.3(a)),  $Z_{C,LC}(f) \approx 50~\Omega$  across a very wide frequency range (Fig. 2.3(b)). Therefore, even with skin effect and dielectric loss, a typical LC-dominant interconnect with  $Z_{C,LC}(f) \approx 50~\Omega$  can be resistively terminated with 50- $\Omega$  resistors like an ideal 50- $\Omega$  transmission line.

Figure 2.4: The simulated LC-dominant channel (Fig. 3(a)) loss versus the frequency when the channel length is 10 cm. Dominant sources of the loss are marked in (b).

Although skin effect and dielectric loss barely change  $Z_{C,LC}(f)$ , they greatly increase the channel loss. By substituting (2.20) and (2.21) into (2.9), we can approximate transfer function  $V_{RX}(l,f)/V_{TX}(f)$  of an LC-dominant channel with skin effect and dielectric loss:

$$\frac{V_{RX}(l,f)}{V_{TX}(f)} \approx \frac{Z_0}{Z_{TX}(f) + Z_0} 2e^{-l(j2\pi\sqrt{LC}f)} \frac{Z_{RX}(f)}{Z_0 + Z_{RX}(f)} \times e^{-l(\frac{R_s}{2Z_0})\sqrt{f}} e^{-l(\frac{G_dZ_0}{2})f}

= TF_{wo}(f) \times e^{-l(\frac{R_s}{2Z_0})\sqrt{f}} e^{-l(\frac{G_dZ_0}{2})f},$$

(2.22)

where  $TF_{wo}(f)$  is the transfer function of an LC-dominant channel without skin effect and dielectric loss. It is noticeable that the channel loss contribution  $e^{-l(\frac{R_s}{2Z_0})\sqrt{f}}$  by the skin effect as well as the channel loss contribution  $e^{-l(\frac{G_dZ_0}{2})f}$  by the dielectric loss are multiplied to the transfer function  $TF_{wo}(f)$  in (2.22). In a typical LC-dominant channel, the first skin-effect term is approximately proportional to the length l and  $\sqrt{f}$